# EPISTAR

## > Mechanical Specification:

- (1) Dimension

- Chip size: 20 mil x 20 mil (500±25 μm x 500±25 μm)

- Thickness: 8.8 mil (225±25 μm)

- N bonding pad: 4.5 mil (115±10  $\mu m)$

#### (2) Metallization

- Topside N electrode: Au alloy

- Backside P electrode: Au alloy

#### Features:

- · Long-term supply

- $\cdot$  High luminous intensity

- $\cdot$  Thin film structure

- $\cdot$  Vertical electrode

- $\cdot$  High driving current

#### **Applications:**

Automotive

N-electrode

\_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_

. . . . . . . . .

Si-substrate

P-electrode

## > Electro-optical Characteristics at 25°C:

| Parameter                            | Symbol |     | Condition  | Min. | Тур. | Max. | Unit |

|--------------------------------------|--------|-----|------------|------|------|------|------|

| Forward Voltage                      | Vf1    |     | lf = 10μΑ  | 1.3  | -    | -    | V    |

|                                      | Vf2    |     | lf = 150mA | -    | 2.3  | 2.8  | V    |

| Reverse Current                      | lr     |     | Vr = 25V   | -    | -    | 5.0  | μΑ   |

| Peak Wavelength                      | λр     |     | lf = 150mA | -    | 631  | -    | nm   |

| Dominant Wavelength <sup>(1)</sup>   | λd     |     | lf = 150mA | 619  | 624  | 629  | nm   |

| Spectra Half-width                   | Δλ     |     | lf = 150mA | -    | 20   | -    | nm   |

| Luminous Intensity <sup>(2)(3)</sup> | lv     | H10 | If = 150mA | 5300 | -    | -    | mcd  |

|                                      |        | H11 |            | 6300 | -    | -    |      |

Note:

(1) Basically, the wavelength span is 10nm; however, customers' special requirements are also welcome.

(2) Customers' special requirements are also welcome.

(3) Luminous intensity is measured by EPISTAR's equipment on bare chips.

#### ES-VMHRPN20R AlGaInP PN-series LED Chip

# > Absolute Maximum Ratings<sup>(1)</sup>:

| Parameter                                 | Symbol           | Condition                   | Rating      | Unit |

|-------------------------------------------|------------------|-----------------------------|-------------|------|

| Forward DC Current                        | lf               | Ta = 25°C                   | ≤ 200       | mA   |

| Reverse Voltage                           | Vr               | Ta = 25°C                   | ≤ 10        | V    |

| Junction Temperature                      | Tj               | -                           | ≤ 125       | °C   |

| ESD withstand voltage(HBM) <sup>(2)</sup> | V <sub>ESD</sub> |                             | Up to 2     | kV   |

|                                           |                  | Chip                        | -40 ~ +85   | °C   |

| Storage Temperature                       | Tstg             | Chip-on-tape/storage        | 5 ~ 35      | °C   |

|                                           |                  | Chip-on-tape/transportation | -20 ~ +65   | °C   |

| Temperature during Packaging              | -                | -                           | 280(<10sec) | °C   |

Note: (1)Maximum ratings are package dependent. The above maximum ratings were determined using a Metal Core Printed Circuit Board (MCPCB) without an encapsulant. Stresses in excess of the absolute maximum ratings such as forward current and junction temperature may cause damage to the LED.

(2)According to ANSI/ESDA/JEDEC JS-001

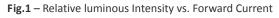

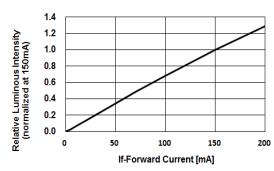

# > Characteristic Curves:

Fig.3 – Relative Intensity (@150mA) vs. Ambient Temperature

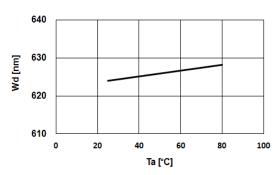

Fig.5 – Dominant Wavelength (@150mA) vs. Ambient Temperature

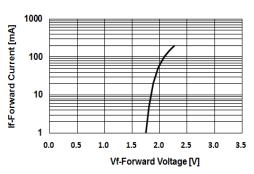

Fig.2 – Forward Current vs. Forward Voltage

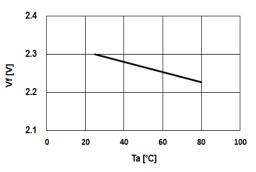

Fig.4 – Forward Voltage (@150mA) vs. Ambient Temperature

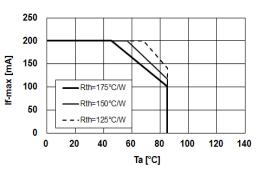

Fig.6 – Maximum Driving Forward DC Current vs. Ambient Temperature (De-rating based on Tj max. = 125°C)

## > Qualification :

- <sup>1)</sup> EPISTAR's LED chips and epi-wafers are designed and manufactured according to the quality management system that complies to the ISO/TS 16949:2009 requirements (IATF No: 0194279/ Certificate Registration No: 20000908 TS09).

- <sup>2)</sup> The chip qualification test plan is based on the guidelines of AEC-Q101-REV-D , Failure Mechanism Based Stress Test Qualification for Discrete Semiconductors in Automotive Applications.

### > Revision :

| Version | Page | Subjects        | Date of Modification |

|---------|------|-----------------|----------------------|

| A       |      | Initial Release | Mar. 2017            |